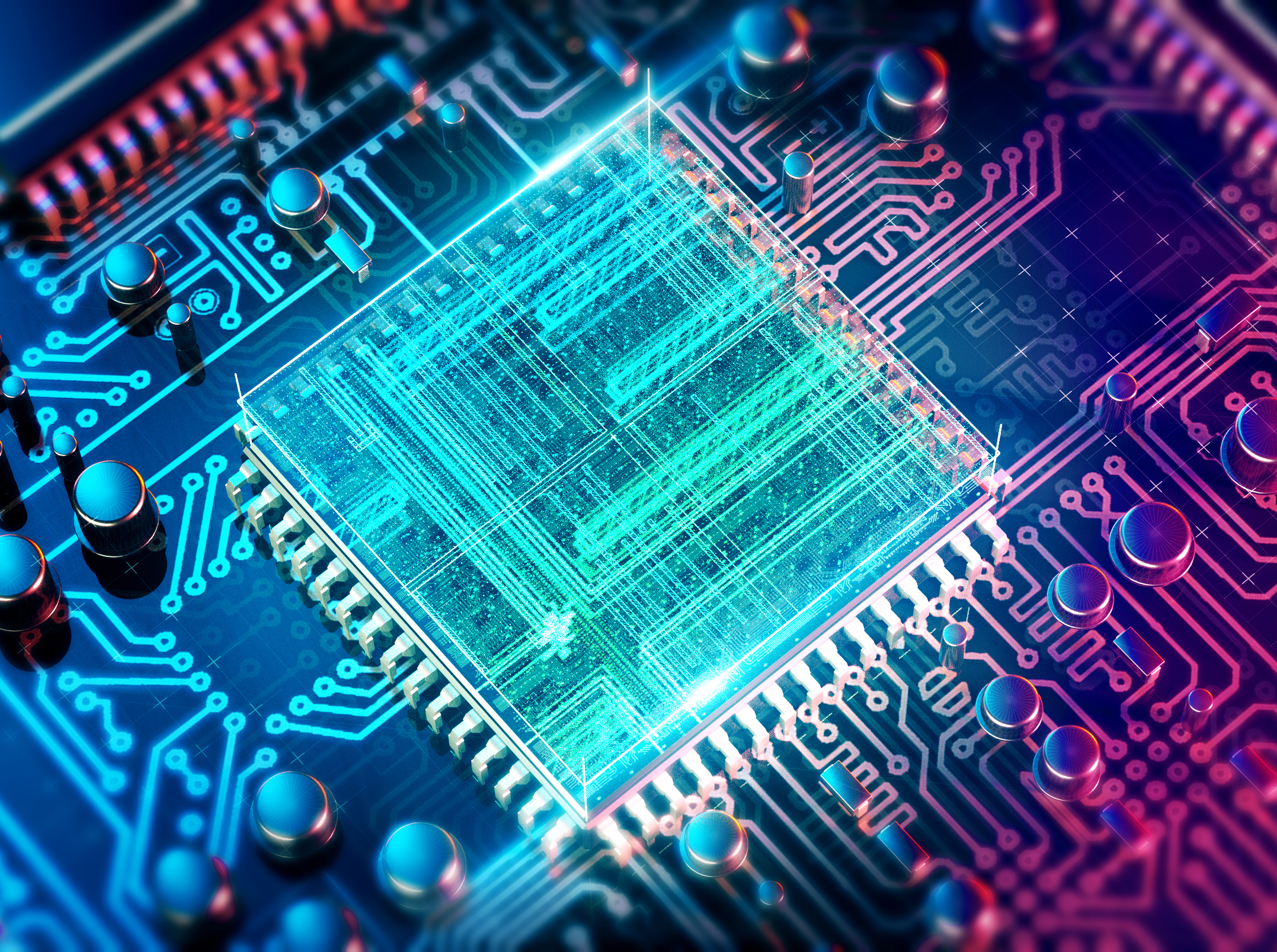

Diseño ASIC

Transformando el proceso de innovación

Explorando, profundizando y aplicando tecnologías de vanguardia en áreas como la automatización, la ciencia de datos y el Internet de las cosas, INTERA apuesta firmemente por el desarrollo de soluciones de IA embebida y aceleradores centrados en optimizar el rendimiento computacional, con el objetivo de crear aplicaciones más eficientes y hacer que la inteligencia artificial sea más accesible para las personas.

Diseño ASIC

Estamos especializados en el diseño ASIC, la verificación y el software embebido, ofreciendo soluciones adaptables que garantizan un desarrollo exitoso.

En INTERA ofrecemos un enfoque integral para el diseño de ASIC digitales. Gracias a servicios como el diseño y verificación RTL, el procesamiento de ASIC y el diseño físico completo, estamos plenamente capacitados para asistir a clientes de diversos sectores en el desarrollo de chips ASIC digitales personalizados

Nuestro diseño de ASIC tiene en cuenta:

Especificación y requisitos

Este paso implica una colaboración estrecha con el cliente para recopilar y aclarar sus necesidades, desglosando las especificaciones generales del producto en requerimientos detallados.

Durante esta fase, reunimos especificaciones técnicas concretas que definen con precisión las características, funcionalidades y criterios de rendimiento del producto, incluyendo resultados esperados, objetivos de rendimiento y metas de consumo energético, sirviendo como guía para el equipo de desarrollo.

Architecture design

During this step we determine the overall structure, the arrangement of functional blocks, and the interconnections between these blocks.

At INTERA this is a crucial step in the design process, as it sets the foundation for the successful integration and operation of the system.

Diseño RTL

Ponemos especial énfasis en la fase de diseño a nivel de transferencia de registros (RTL), ya que es una etapa crucial en el desarrollo ASIC.

Mediante el uso de lenguajes de descripción de hardware (HDL), nuestros diseñadores definen la lógica, el temporizado y la arquitectura del circuito digital, lo que permite su simulación y síntesis para su posterior implementación en silicio.

Verificación

Consideramos la verificación como una etapa clave en nuestro proceso de diseño ASIC, ya que implica pruebas y validaciones exhaustivas para confirmar que el diseño cumple con los requisitos especificados.

Durante esta fase, realizamos simulaciones, métodos de verificación formal y pruebas en hardware para detectar y corregir posibles discrepancias, asegurando que el ASIC funcione correctamente y cumpla con los objetivos de rendimiento, temporización y consumo energético antes de pasar a producción.

Síntesis e implementación

Durante la fase de síntesis, convertimos el código RTL en una netlist a nivel de compuertas, que representa la implementación física del ASIC.

Para optimizar el diseño físico en cuanto a bajo consumo energético, máxima velocidad y uso eficiente del área, traducimos la netlist en un layout. Este proceso incluye la colocación de los componentes, el enrutamiento de las conexiones entre ellos y la aplicación de reglas de diseño que garanticen su fabricabilidad.

Cierre de diseño y tape-out

Una vez completado el diseño físico, es fundamental realizar una verificación de reglas de diseño (DRC) para asegurar que el layout cumple con las especificaciones y normas establecidas por la fundición.

Este proceso de verificación consiste en analizar el diseño para garantizar el cumplimiento de requisitos específicos de ancho, espaciado y capas, con el fin de evitar defectos de fabricación y asegurar un rendimiento óptimo.

Fabricación

Durante esta etapa colaboramos con las fundiciones encargadas de producir el chip diseñado a medida.

¿Problema resuelto?

Nuestro diseño ASIC resuelve problemas relacionados con el rendimiento, la eficiencia y la especialización en electrónica mediante la creación de chips personalizados adaptados a tareas específicas. A continuación, se detallan los principales problemas que aborda el diseño de ASIC:

Cuellos de botella en el rendimiento

Problema: Los chips de propósito general desperdician ciclos en operaciones innecesarias o presentan dificultades con la latencia en tareas exigentes como la criptografía, la inferencia en aprendizaje automático o el procesamiento de señales.

Consumo de energía

Restricciones de tamaño y espacio

Problema: Integrar componentes electrónicos de alto rendimiento en formatos muy reducidos, como dispositivos wearables o sensores IoT, resulta complicado al utilizar chips voluminosos y de propósito general.

Costo a escala

Problema: Los chips comerciales pueden volverse costosos cuando se implementan en grandes cantidades, especialmente si incluyen funciones que no se necesitan.

Solución ASIC:

Al cablear la lógica para una función específica, nuestros diseños de ASIC eliminan la sobrecarga, ofreciendo una ejecución extremadamente rápida. Nos aseguramos de optimizar los flujos de datos y las velocidades de reloj según la carga de trabajo concreta.

Solución ASIC:

Nuestros diseños personalizados eliminan circuitería irrelevante, lo que minimiza el consumo energético. Los ajustamos para ejecutar únicamente lo necesario, reduciendo el uso de energía en un 60 % en comparación con otras alternativas del mercado.

Solución ASIC:

Los diseños a medida de INTERA reducen el tamaño del chip al centrarse únicamente en los componentes esenciales, lo que permite crear dispositivos compactos y ligeros.

Solución ASIC:

Nos aseguramos de que los costos iniciales de diseño sean justos y estén adaptados a las capacidades del cliente, y también garantizamos que el costo por unidad se reduzca significativamente en producciones a gran escala.

Latencia y procesamiento en tiempo real

Problema: Aplicaciones como los sistemas autónomos requieren una latencia ultra baja que los procesadores genéricos no pueden garantizar de forma constante debido a la sobrecarga del software o al uso compartido de recursos.

Exceso de funcionalidades

Problema: Los chips de propósito general incluyen componentes innecesarios, como unidades de coma flotante o núcleos adicionales, que no se utilizan en aplicaciones específicas, lo que incrementa el costo y la complejidad.

Vulnerabilidades de seguridad

Problema: Los chips estándar pueden ser explotados mediante software (por ejemplo, Spectre/Meltdown) o ser objeto de ingeniería inversa con mayor facilidad debido a su arquitectura predecible.

Límites de escalabilidad en cargas de trabajo especializadas

Problema: A medida que aumentan las cargas de trabajo, como el entrenamiento de modelos de IA o la validación en blockchain, los chips de propósito general alcanzan un límite, lo que obliga a recurrir a agrupaciones de hardware poco prácticas.

ASIC Solution:

Nos aseguramos de que el hardware dedicado ejecute tareas en paralelo con un retraso mínimo, a menudo en microsegundos, lo que permite evitar los cuellos de botella del software.

Solución ASIC:

Nuestra propuesta de ASIC es eficiente, ya que incluye únicamente la circuitería necesaria, lo que simplifica la integración y mejora la fiabilidad.

Solución ASIC:

Nuestros diseños personalizados pueden incorporar funciones de seguridad exclusivas, como cifrado por hardware o lógica a prueba de manipulaciones, lo que dificulta y encarece los intentos de ataque.

Solución ASIC:

Nuestros ASICs escalan de forma eficiente dentro de su nicho, ofreciendo incrementos de rendimiento lineales sin necesidad de complejas configuraciones con múltiples chips.

DATOS TÉCNICOS

INTERA está formada por los profesionales más comprometidos de Europa, quienes colaboran con los clientes para desarrollar las soluciones de inteligencia artificial y aceleradores de chips más avanzados.

La empresa ha desarrollado soluciones innovadoras para diversas aplicaciones, avanzando el estado del arte y generando valor para sus clientes y socios.