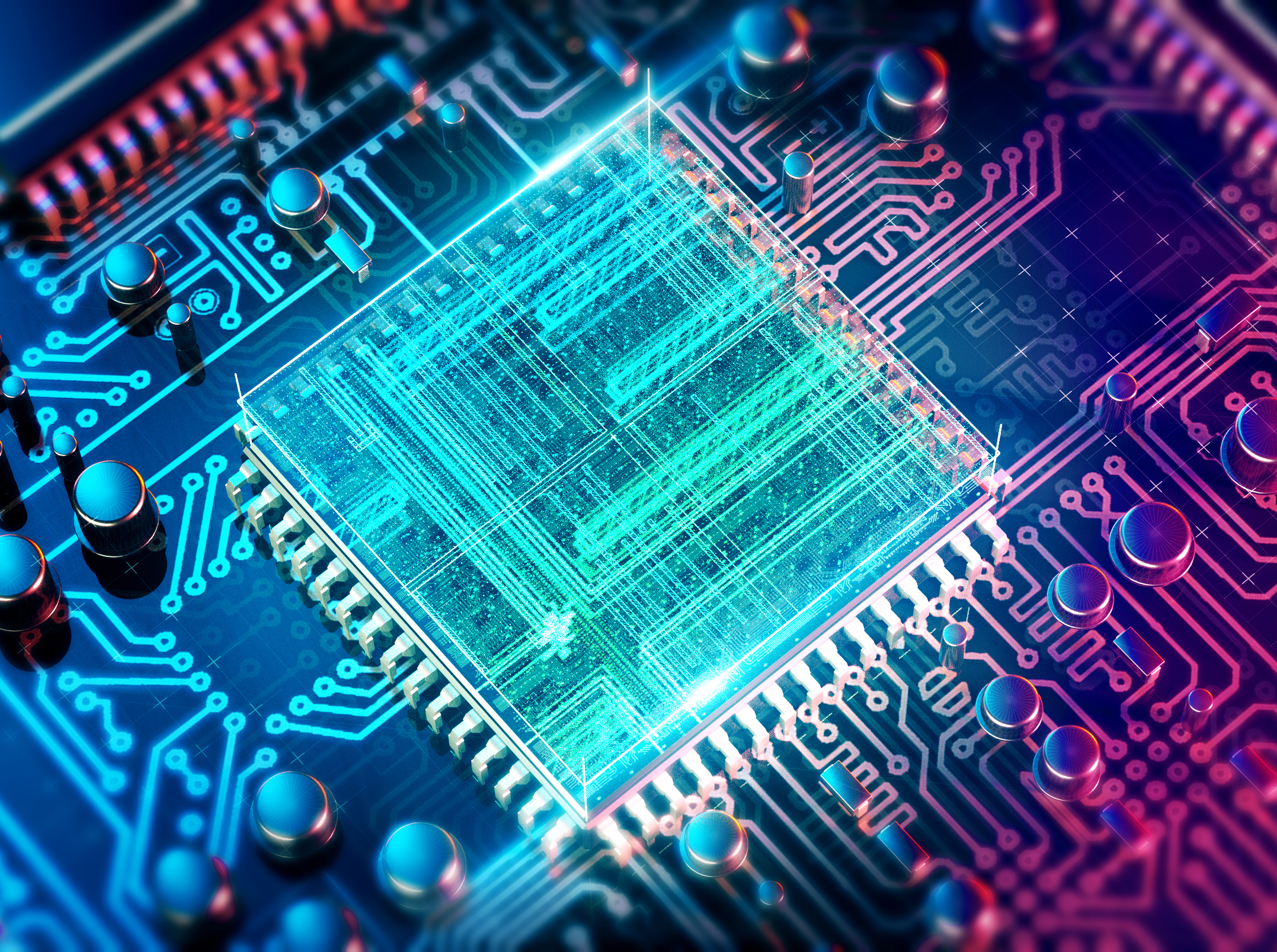

ASIC design

Transforming the process of innovation

Exploring, deepening, and applying cutting-edge technologies in areas like automation, data science and the Internet of things, now INTERA is strongly betting in developing embedded AI solutions and accelerators focusing on optimizing computing performance, to make AI applications more efficient and more accesible to people.

ASIC design

We specialize in ASIC design, verification, and embedded software, delivering adaptable solutions that ensure successful development.

We offer a comprehensive approach to digital ASIC design. By offering services such as RTL design and verification, ASIC processing, and full physical design, INTERA is well-equipped to assist customers in a variety of industries with their custom digital ASIC chip needs.

Our ASIC design considers:

Specification and requirements

This step involves collaborating closely with the client to collect and clarify their requirements and then breaking down the high-level product specifications into detailed.

During this step we gather actionable technical specifications that outline the exact features, functionalities, and performance criteria for the product, expected outputs, performance objectives, power consumption targets, serving as a blueprint for the development team.

Architecture design

During this step we determine the overall structure, the arrangement of functional blocks, and the interconnections between these blocks.

At INTERA this is a crucial step in the design process, as it sets the foundation for the successful integration and operation of the system.

RTL design

We emphasize efforts during Register-Transfer Level (RTL) design as it is a crucial phase in ASIC development.

Utilizing Hardware Description Languages (HDLs), our designers specify the logic, timing, and architecture of the digital circuit, enabling simulation and synthesis for implementation in silicon.

Verification

We consider Verification to be a crucial step in our ASIC design process, as it involves thorough testing and validation to confirm that the design aligns with the specified requirements.

During this phase conduct simulations, formal verification methods, and hardware testing to identify and rectify any discrepancies, ensuring the ASIC functions work correctly and it meets performance targets, timing, and power specifications before moving into production.

Synthesis and implementation

During the synthesis phase, we convert RTL code into a gate-level netlist, representing ASIC’s physical implementation.

To optimize the physical design for low power consumption, maximizes speed, and efficiently utilizes area, we translate the netlist into a layout, this process includes determining the placement of components, routing the connections between them, and applying design rules to ensure manufacturability.

Signoff and tape-out

After completing the physical layout, it is crucial to perform a design rule check (DRC) to ensure that the layout adheres to the foundry’s specifications and design rules.

This verification process involves analyzing the layout for compliance with width, spacing, and layer-specific requirements to avoid manufacturing defects and guarantee optimal performance.

Manufacturing

During this step we will collaborate with the foundries producing the custom-designed chip.

We will work with the foundries by getting involved closely with their engineers to ensure that the custom-designed chip meets the required specifications and is manufactured according to the planned production schedule.

Problem Solved?

Our ASIC design solves problems tied to performance, efficiency, and specialization in electronics by creating custom chips tailored to specific tasks. Following is a breakdown of the key problems ASIC design addresses:

Performance Bottlenecks

Problem: General-purpose chips waste cycles on unnecessary operations or struggle with latency in demanding tasks like cryptography, machine learning inference, or signal processing.

Power Consumption

Problem: Broad-spectrum chips burn energy on unused features, draining batteries or spiking electricity costs e.g. mobile devices or data centers.

Size and Space Constraints

Problem: Fitting high-performance electronics into tiny form factors like wearables or IoT sensors is tough with bulky, multi-purpose chips.

Cost at Scale

Problem: Off-the-shelf chips get pricey when deployed in massive quantities, especially if they include features you don’t need.

ASIC Solution:

By hardwiring logic for a specific function, our ASICs design eliminate overhead, delivering blazing-fast execution. We ensure optimizing data paths and clock speeds for specific workload.

ASIC Solution:

Our customized designs strip out irrelevant circuitry, minimizing power draw. We tuned them to run only what’s needed, slashing energy use by 60% compared to alternatives in the market.

ASIC Solution:

INTERA´S tailored layouts shrink die size by focusing only on essential components, enabling compact, lightweight devices.

ASIC Solution:

We ensure upfront design costs are fare and adjusted to the customer capabilities, we also ensure that final per-unit costs drop significantly in high-volume production.

Latency and Real-Time Processing

Problem: Applications like autonomous systems demand ultra-low latency that generic processors can’t consistently hit due to software overhead or shared resources.

Feature Overhead

Problem: General-purpose chips come with bells and whistles e.g. floating-point units or extra cores that go unused in specific applications, inflating cost and complexity.

Security Vulnerabilities

Problem: Standard chips can be exploited via software (e.g., Spectre/Meltdown) or reverse-engineered more easily due to their predictable architecture.

Scalability Limits in Specialized Workloads

Problem: As workloads grow in AI training or blockchain validation general chips hit a wall, requiring impractical clusters of hardware.

ASIC Solution:

We ensure that dedicated hardware executes tasks in parallel with minimal delay, often in microseconds, in this way we ensure bypassing software bottlenecks.

ASIC Solution:

Our ASICs proposal is lean, including only the circuitry required, which simplifies integration and boost’s reliability.

ASIC Solution:

Our custom designs can embed unique security features like hardware encryption or tamper-proof logic making attacks harder and more costly.

ASIC Solution:

Our ASICs scale efficiently for their niche, delivering linear performance gains without the sprawl of multi-chip setups.

TECHNICAL DATA

INTERA is made up of the most committed professionals in Europe who collaborate with clients to work towards creating the most advanced AI solutions & chip accelerators.

The company has developed innovative solutions for various applications, advancing the state of the art and creating value for its customers and partners.